### **Sales Brochure**

# **Cambridge Consultants ASIC Products**

ASIC processors

**Development tools**

XAP APE SIF xEMU

**x**IDE

These IP blocks and Development Tools have helped Cambridge Consultants and their customers get many mixed analogue-digital SoC ASICs

# Right First Time!

They can help you too...

xIDE kernel +

custom plugin

create a friendly

Integrated

Development

Environment for

software on the

Final Product or

Emulator

Final

Product

**ASIC**

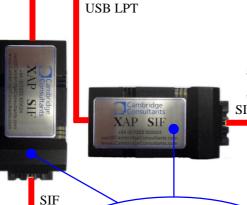

SIF pods enable highspeed, real-time noninvasive software debug and data acquisition

xEMU ASIC Emulator implements all the digital parts of the ASIC (gates, memories) and interfaces to a custom daughter card for all the analogue parts

XAP C Processor

APE DSP Processor Analogue IP

Cambridge Consultants

C4862-SB-002 v0.7 22 April 2004 Cambridge Consultants Ltd Science Park Milton Road Cambridge England CB4 0DW Tel: +44 (0) 1223 420024 asic@CambridgeConsultants.com www.CambridgeConsultants.com

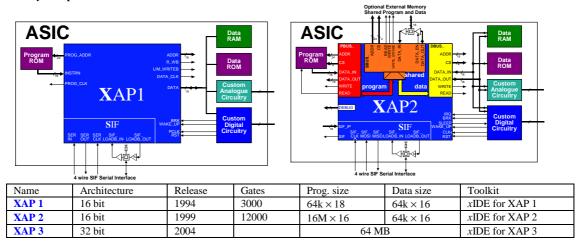

### **ASIC Processors**

XAP family of C processors

All the XAP family processors are optimised for ASIC use. They are low power, low gate count processors that offer high code density, minimising the cost of on-chip and off-chip memories (RAM, ROM, Flash). They come with full software development toolkits based upon xIDE. The C compiler, Assembler, Linker, Software Simulator and documentation, are available for a 1 month free trial download from <a href="https://www.cambridgeconsultants.com/asic">www.cambridgeconsultants.com/asic</a>.

#### **APE DSP Processor**

### APE2 Customisable DSP Processor

Ideal for the low power, low gate count implementation of DSP algorithms. Has been proved in software radio applications. It is frequently used as a co-processor for the XAP family

## **Development Tools**

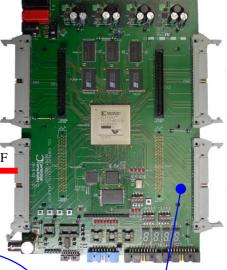

### xEMU ASIC Emulator

Contains; large Xilinx FPGA that can emulate up to 300k gates of random logic, 3 4Mbit RAM, 3 4Mbit Flash, JTAG port for configuration, SIF connection for debug and Control, multiple IO ports and daughter card connections. The xEMU allows ASIC designs to be precisely emulated at all levels, providing a very high level of confidence in the design before chips are manufactured. It also allows you to see the complete product working with real sensors or radio in a real life test environment.

#### **SIF** Serial Interface

A patented 4 wire Serial interface developed by CCL . It allows non-invasive control and debug. Provides complete access to memory and registers without interfering with the chip operation or timing. It is available with USB or LPT PC interfaces. The Windows drivers enable multiple applications to simultaneously access all memory mapped devices in the ASIC using a single SIF Pod.

#### **x**IDE Integrated Development Environment

*x*IDE is an Integrated Development Environment designed with the standard look and feel of IDE packages on the PC. Cambridge Consultants can develop custom plugins for different processors, ASICs and complete products. Plug-in support exists already for the XAP family of C processors and several ASICs created by CCL.

# Analogue IP

Cambridge Consultants has an extensive range of analogue building blocks including RF and ADC components that greatly accelerate the design of mixed mode ASICs

### References

Cambridge Silicon Radio (<u>www.csr.com</u>) use the XAP2 in all their Bluetooth chips. They also use software toolkits based on *x*IDE for their Bluetooth products.

XAP SIF