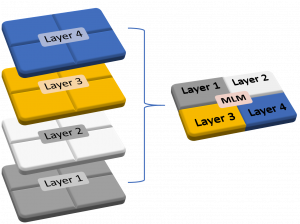

These are some of the advantages of a MLM run:

- lower mask costs

- an MLM run is organized for one customer

- it can be scheduled for any date since it does not depend on regular MPW runs

- a customer receives a few wafers, resulting in a few hundreds of prototypes

The MLM technique is preferred over MPW runs when the chip area becomes large and when the customer wants to get a higher number of prototypes. If the prototypes are successful, the mask set can be used under certain conditions for low volume production.

MLM runs are only available for technologies from ON Semiconductor, IHP, GLOBALFOUNDRIES and XFAB.