This service has been developed to help lower the barriers to entry and encourage the adoption of chiplet-based packaged modules that provide easy electrical access to their integrated circuits.

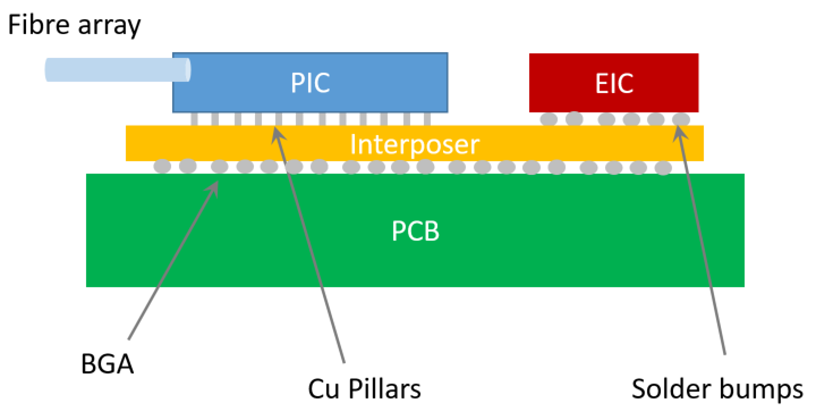

The service includes flip-chip bonding of user chips onto a single layer silicon interposer. If users are interested in a packaged module, the interposer can also be flip-chip bonded to a standardised PCB which can then be further assembled in a standard mechanical housing. The components and processes are standardised, allowing users to access their ICs without the need for customised designs. The layout and routing on the silicon interposer will be customised for the user’s ICs.

For further details, please refer to the Chiplet Integration Design Rules:

Chiplet Integration – Standard Si Interposer Package Summary | |

|---|---|

Integration | 2.5D integration |

Electrical connection | Flip-chip bonding |

Connection material chiplet to interposer | Gold stud bumping and coining |

Connection material interposer to PCB | Low-melting Bismuth-Tin (Bi-Sn) |

Interposer material – no. of layer – size | Silicon – single layer – 30 mm × 30 mm |

Interposer DC connections | Maximum 260 DC |

Number of chiplets | As many as fit on interposer |

PCB connections | Maximum 260 DC – 4 Connectors |

Mechanical housing dimensions (with holes) | 92 mm × 74 mm × 8.3 mm |

If you are interested, please complete the EUROPRACTICE-Chiplet-Initial Enquiry Form and send it to marc.rensing@tyndall.ie.

We will provide you with more information about our offer and pricing options.

Please note that each service will have different pricing depending on the materials and processes.

Micro-Transfer Printing (MTP) is a heterogeneous integration technique that enables devices from one material system to be transferred from their native substrate to a host substrate of a different material. MTP uses a PDMS stamp to collect the devices from the original wafer and releases them to the target substrate.

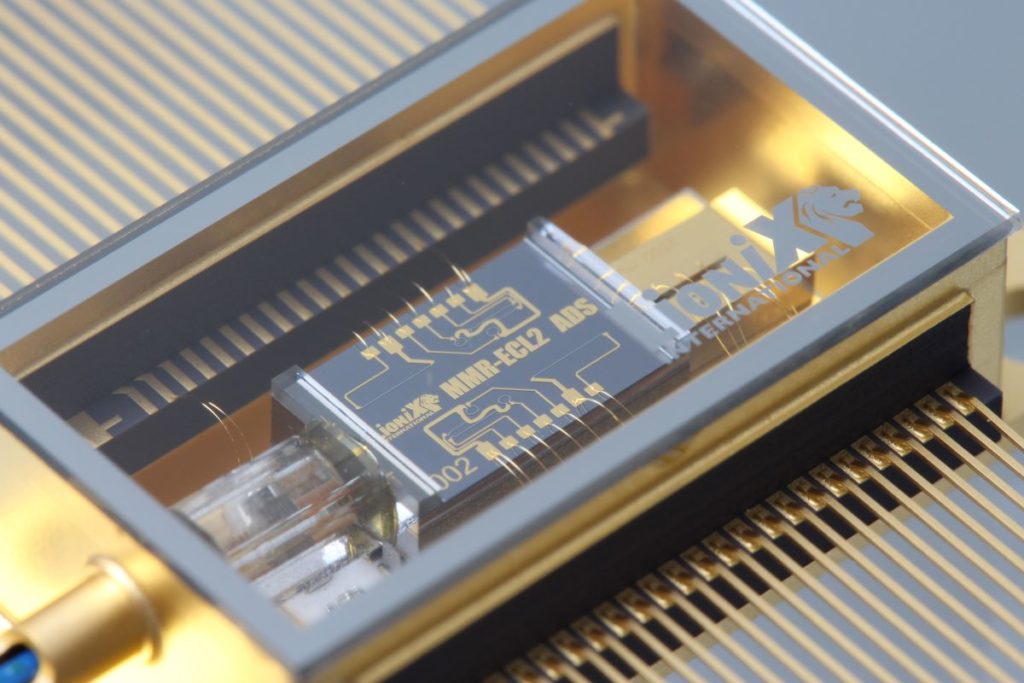

With this service, users can create packaged MTPbased optical chiplet modules. It supports the integration of InP lasers or UTC photodiodes onto silicon platforms. The processes and components are standardised, so users can access the component without the need for customised designs. The details of the laser coupon are given in our Chiplet Integration Design Rules.

Tyndall offers a standard etched facet edge emitting laser for transfer print onto either silicon submounts designed and supplied by Tyndall or users can provide their own substrates or PICs.

As the lasers require a target to be printed onto, Tyndall have fabricated Si based submounts measuring 5mm x 5mm, allowing 4 lasers to be transfer printed at a pitch of 250µm to match the pitch of standard fiber arrays. RDL lines allow for wire bonding and electrical connections to an external PCB. These can then be optically coupled and packaged into a standardised package allowing easy optical and electrical access. Users may also supply their own compatible platform for printing.

For Europractice users, Tyndall has designed a standard UTC Photodiode (PD) and offers its printing onto either Tyndall substrates or provided by those requesting the service. The UTC PD is InP based with a maximum thickness of 1.2µm. It can detect light ranging in wavelengths from 950 to 1550 nm. The maximum frequency at which this device can operate has been measured up to 90 GHz, measured though probe testing.

Tyndall provide different packaging options for the transfer printed devices including:

To allow users to move from prototyping volumes and scale-up to production levels, a mass chiplet micro transfer print service will be made available in 2025.

If you are interested, please complete the EUROPRACTICE-MTP- Initial Enquiry Form and send it to marc.rensing@tyndall.ie.

We will provide you with more information about our offer and pricing options.

Fraunhofer and CIME-P, in partnership with ams OSRAM, offer advanced 2.5D integration using silicon interposer technology. This enables side-by-side integration of heterogeneous chiplets with higher interconnection density compared to organic substrates, contributing to a reduced package footprint, increased inter-die bandwidth, and lower power consumption.

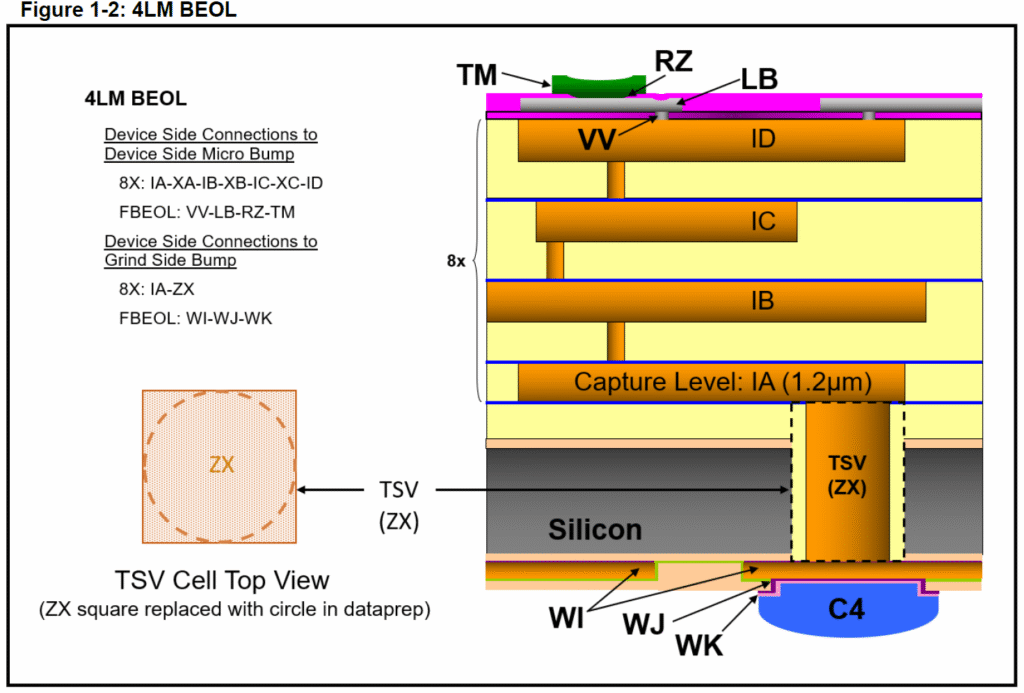

This interposer solution is built on the C35B4 (0.35 μm) process, featuring four metal layers, with an optional thick top layer for enhanced routing. For customers planning flip-chip assembly, we offer a post-process under-bump metallization (UBM) option.

Additionally, wire bonding is supported, allowing the interposer to connect to a PCB (chip-on-board) or a compatible package. A representative schematic is shown below.

Two interposer types are available under this service offer:

Because the fabrication process is based on the C35B4 technology, users benefit from a mature and reliable platform. In addition to the standard CMOS-oriented DRM, ams OSRAM provides assembly-related design rules, as well as WLCSP (Wafer-Level Chip Scale Packaging) guidelines for RDL and UBM modules.

Since 2025, a new commercial offer has been introduced featuring MPW runs dedicated to the passive interposer version of the ams OSRAM C35 technology. While this technology was previously available to Europractice users, the new offer provides an enhanced opportunity for access through more cost-effective runs that use a limited number of masks.

In addition, Through-Silicon Vias (TSVs) are now available for MPW runs for the passive interposers, where a proof of volume production was previously required. This development represents a significant step forward in broadening advanced packaging and system integration options for the Europractice community.

Jeremy Perret

Tel: +33 (0)4 56 52 94 30

jeremy.perret@grenoble-inp.fr

Elvira Liandres

Tel: +49 (0)9131 776 4464

silicon-asic@iis.fraunhofer.de

Fraunhofer IIS, in partnership with GlobalFoundries, offer silicon interposers manufactured on GlobalFoundries’ 65 nm technology node, enabling advanced 2.5D packaging solutions for chiplet-based architectures.

These 65 nm interposers incorporate through-silicon vias (TSVs) and redistribution layers (RDLs) to support fine-pitch interconnects and high-density routing. This allows integration of multiple dies within a compact, high-performance package, delivering improved functionality and system complexity.

By leveraging a proven and scalable platform, GlobalFoundries’ 65 nm interposer process enables heterogeneous integration, reduces power consumption, and enhances overall system performance. Please note this service is only offered as a dedicated engineering run.

Syed Shahnawaz

Tel: +49 (0)9131 776 4425

virtual-asic@iis.fraunhofer.de

Fraunhofer ISS, in partnership with the Leibniz Institute for High Performance Microelectronics (IHP), offer advanced silicon interposers based on IHP’s IntM4TM technology. These interposers feature two thin and two thick Al-BEOL layers on a high-resistivity substrate, delivering exceptional electrical performance.

The technology integrates high-density through-silicon vias (TSVs) and fine-pitch wiring, making it ideal for high-frequency and high-performance computing applications. It enables seamless integration of heterogeneous components, such as processors, memory, and RF modules, optimising system performance and reducing latency.

Designed for scalability and compatibility with modern packaging standards, the interposer supports industries including telecommunications, automotive, and IoT.

Tyndall offers a single-layer silicon interposer solution designed to enable the integration of multiple electronic ICs on a common silicon platform. This service includes:

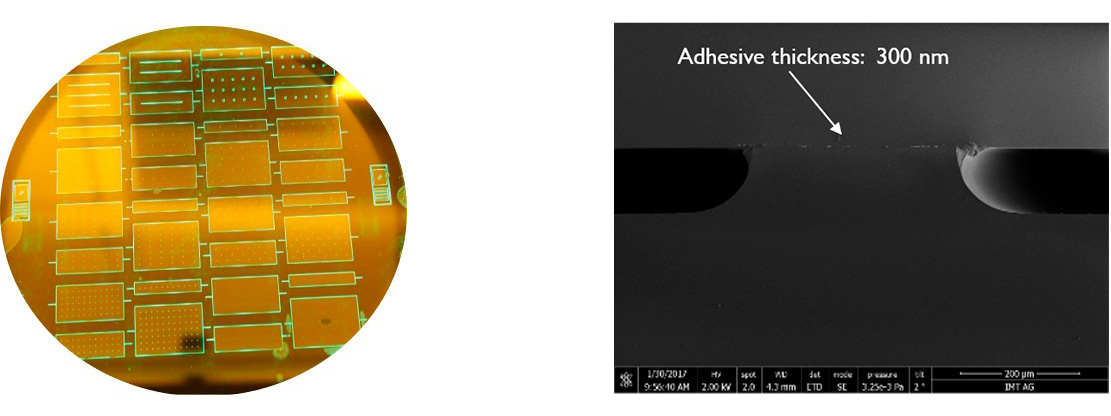

The interposer is manufactured in Tyndall’s cleanroom on 100 mm wafers, delivering a minimum of four interposers per run. Each interposer measures 30 mm × 30 mm × 0.5 mm and supports up to 260 DC-only connections, routed via 1 µm gold-metallised tracks. These tracks connect micro-bond pads to larger C4 bond pads along the periphery.

This fabrication service is offered in conjunction with our Electronic IC Integration onto Silicon Interposers and Module Packaging service, providing a complete solution for advanced electronic integration.

Interposer Design Rules | |

|---|---|

Material | Silicon |

Size | 30 mm × 30 mm |

Total DC connections | 260 |

Metallization (Single Layer) | AU |

Metallization thickness | 1μm |

Microbump pad pitch | 55μm |

C4 bump pad pitch | 155-255μm |

This service is accessible for all Europractice customers. It is provided by our partner Fraunhofer.

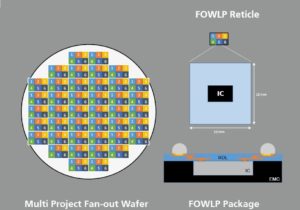

Multi-Project Fan-Out Wafer Level Packaging | |

|---|---|

Design Rules & Materials | Multi-project wafer processing is an established approach in semiconductor manufacturing for fast and low-cost prototyping. This idea is now transferred to fan-out wafer level packaging. Here dies from different sources or different technologies with varying thickness and size can be handled and packaged with one integration technology. This offers a path to a well adopted technology, especially for RF applications. |

MPFOWL Package Specification | Die delivery: WafflePack, wafer, wheel Die size: 1.5 – 7 mm edge length Die thickness: 200 – 300 μm Package thickness: 450 μm Package size: 10×10 mm², smaller package size possible with extra effort Metal layers: 2 Integration of e.g. antennas and passive structures in RDL Pin-out: BGA – Pitch: 500 μm – Ball size: 300 μm – Solder: SnAgCu Defined packaging materials |

Description of Services | – Engineering service including one time design rule check (DRC) – Early Access Engineering run (production and delivery of untested packages) Packaging in Multi-Project Fan-out Wafer Level Technology according to Design Rules IZM The services are subject to that the Client provides Fraunhofer IZM with the following information/goods: – FOWLP package design according Design Rules IZM (“Layout”) – Chips to be processed including 5 to 10 set-up chips |

The manufacturing will be done in a mold-first face-down flow with the following steps: | |

Die assembly on a temporary carrier | |

| Overmolding and generation of the multi project reconfigured substrate |

Release from the temporary carrier | |

• 1st Pi passivation layer generation in a wafer-level process • 1st copper layer generation – PVD & galvanic deposition | |

| • 2nd Pi passivation layer generation • 2nd copper layer generation – PVD & galvanic deposition |

| 3rd Pi passivation layer generation |

| Solder Ball generation |

| Singulation by dicing |

You can find more details in the MPFOWLP flyer

Dr. Tanja Braun

e-mail: europractice@izm.fraunhofer.de

Fraunhofer Institute for Reliability and Microintegration IZM

Here you can download NDA for this technology.

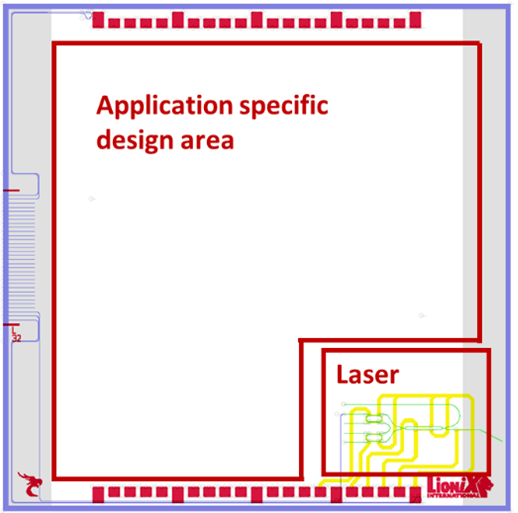

Laser Integration for LioniX SiN-Photonics | |||

|---|---|---|---|

Tyndall, in partnership with LioniX International, offers laser integration to Silicon Nitride MPW runs. The tunable laser building block provides the user with a narrow linewidth source with specifications given in the table below. As with all other building blocks offered in LioniX PDK, it allows the user to easily connect the items together and create a customized or application specific design. | |||

Wavelength Tuning Range | On-Chip Power | Linewidth | |

Tunable Laser Building Block | C-band | >1 mW | <100 kHz |

By offering the tunable laser building block, the MPW user can get access not only to LioniX’s well known low-loss waveguide platform TriPleX™, but also to the unique integration of an InP gain section to the PICs all through using a designer PDK. • This is a post-process following an MPW run. • Dedicated runs are possible and can be made available by agreement. Please contact Tyndall for more information/quotation. | |||

Application area | Telecoms/Datacom, C-band | ||

Technology | Telecoms/Datacom, C-band | ||

PDK Manual | Available upon request | ||

Packaging | Available upon request | ||

Marc Rensing

e-mail: marc.rensing@tyndall.ie

Microfluidic system integration | |

|---|---|

This service is accessible to all Europractice customers.

Allows to integrate microfluidic functionalities on top of Si CMOS sensor technology with noble metal top surface finish by means of wafer-level glass microfluidics. These technology combinations are suited for the fabrication of chemical, bio-chemical and medical devices but could also be of potential interest for high power applications that need liquid cooling for thermal management. | |

Building blocks | Si CMOS with noble metal sensor technology (add-on on X-FAB XH035) Multi-layer glass wafer fabrication Si-to-glass wafer-level bonding, key features: – room temperature bonding for encapsulation of bio-materials – ultra-thin selective adhesive transfer technology with excellent uniformity over large areas – compatible with a wide range of materials, e.g. CTE – compatible to wide range of P, T, pH – abundance of Adhesives to suit customer assay – bio-compatibility assured |

Design rules | The combination of these building blocks provides you an integrated solution of a Si CMOS sensor chip with micro-scaled glass microfluidic functionalities in direct contact with the Si surface. Additional routing layers inside the glass interposer chip may facilitate the further integration to macro-sized fluidic interfaces. Apart from the individual building block design rules, specific rules apply for the integration. Electrical access is provided through wire bonding and fluidic connection is realized through standard-sized fluidic access holes |

| |

Fraunhofer and CIME-P provide access to this ams OSRAM technology.

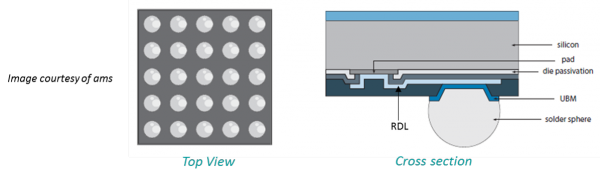

ams 0.35µm wafer-level bumping | |

|---|---|

Technology characteristics | Solder bumping consists in manufacturing metal spheres acting as interconnections for flip-chip. Those spheres are composed of a Sn/Ag/Cu alloy (SAC). Before the sphere can be deposited, the deposition of an Under Bump Metalization (UBM) layer is required.

This option, available on ams 0.35 runs only, is operated at wafer-level within ams cleanroom after CMOS process. It allows the deposition of an array of solder balls at wafer-level, with an I/O pitch compatible with traditional printed circuit board (PCB) assembly processes. For mechanical reasons solder balls are usually evenly distributed over the whole chip surface and electrically connected to the IC‘s CMOS pads by means of a redistribution layer (RDL) included in the option. |

Application area | Single die flip-chip packaging |

Design Kit version | Option supported by ams hitkit 4.10 ISR15, through an add-on |

Europractice offers advanced fibre attaches. This includes single-mode optical fibre (SMF), polarization-maintaining optical fibre (PMF), single fibre and arrays, as well as single lensed fibre. You can find detailed information on the Photonic Packaging page

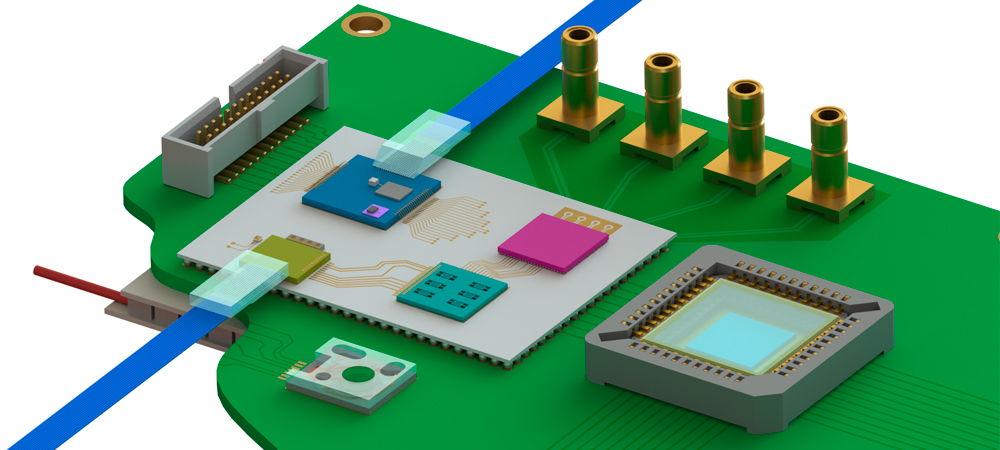

System integration is the challenge of combining devices from different technologies on the same platform or in the same package.

It is used in a wide variety of technologies, such as microelectronics, optics, photonics, MEMS, microfluidics and combinations of these put together, also known as Hybrid Integration.

Examples of system integration in the semiconductor industry are vast, such as high-speed high-density Datacom transceivers, compact high-speed telecom receivers and bio-medical sensors to name a few.

Chiplet integration allows the functionality of large chips to be partitioned into smaller dies which can then be interconnected together using standard packaging processes within a package or common substate to build a heterogenous system.

Packaging technologies play a key role in heterogeneous integration and chiplet based designs can be built on different materials such as silicon, glass or PCBs. The outcome is a quick, low cost and high-performance integration approach.

We speak about System Integration when we combine at least two devices stacked and interconnected, or packaged side-by-side on a substrate.

Both chiplet & system integration are made possible through accessing a variety of specialised services of key enabling technologies. This includes, flip-chip bonding, wire-bonding, stud bumping, solder jetting, Ball Grid Arrays (BGAs), wafer-level fan-outs as well as silicon interposers. These technologies facilitate 2.5/3D integration of electronic devices, such as ASICs, as well as Photonic Integrated Circuits (PICs).

You can explore these solutions in our offer below.

System Integration opens up new technology and application possibilities. This can be beneficial on many levels, from energy savings through lower power consumption, to faster data rates, better signal integrity and smaller footprints.

Chiplet integration, from a design perspective offers higher yields, reduced development times and costs through reusable IP and the opportunity to mix technologies/components, in a mix and match approach.